jks

About

- Username

- jks

- Joined

- Visits

- 36,739

- Last Active

- Roles

- Member, Administrator, Moderator

- Points

- 670

Reactions

-

10ch receiver mode ?

-

10ch receiver mode ?

-

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

I didn't mention this, but the new Ethernet speed setting is "sticky". So when the Beagle is powered-up or rebooted the Ethernet will come up in 100 Mbps mode by default. But when the Kiwi server starts and sees 10 Mbps mode has been set in the configuration it will change the interface speed back down to 10.

There is also a new Linux command 'e' that is an alias for 'ethtool eth0' to show the interface state including the speed setting. Also 'e10' and 'e100' for manually setting the speeds. -

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

I didn't mention this, but the new Ethernet speed setting is "sticky". So when the Beagle is powered-up or rebooted the Ethernet will come up in 100 Mbps mode by default. But when the Kiwi server starts and sees 10 Mbps mode has been set in the configuration it will change the interface speed back down to 10.

There is also a new Linux command 'e' that is an alias for 'ethtool eth0' to show the interface state including the speed setting. Also 'e10' and 'e100' for manually setting the speeds. -

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

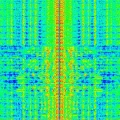

Three channels at 20 kHz is subject to being reduced to only two depending on experiences with stability. I would have set it at two but I couldn't get the FPGA code to compile using only two channels for reasons I still don't understand. From the CHANGE_LOG file:v1.250 December 31, 2018 Add 20 kHz wide audio bandwidth mode. A third entry to the list of FPGA configurations. See admin "mode" tab for details. Add Ethernet 10/100 speed select to admin network tab. The speed changes after a few seconds of delay (no Kiwi restart required). This allows you to be looking at a waterfall in another window and see if the Ethernet spurs (if present at your installation) improve or not. Be sure the device (router, switch) your Kiwi connects to supports 10 Mbps Ethernet. Accept 'k' & 'M' scaling suffixes in frequency and passband parameters. Examples: Type "/15k" in frequency box to get a 15 kHz wide passband. Or "/2.7k", "-5k,10k" etc. Use a URL of "...?f=7.4M/16.5k" to set a frequency of 7.4 MHz and passband of 16.5 kHz. Note uppercase 'M' since 'm' is already keyboard shortcut for mute. You can remember this because the 'M' in MHz is always capitalized whereas 'k' in kHz is not. Note also 'k' used to be paired with 'j' as the frequency up/down jog shortcut. Now use the 'j' and 'i' keys are used (also 'J' and 'I' to jog faster). Using the 'i' key is actually more natural because it fits the placement of your index and middle fingers better than 'j' and 'k'. Finally, 'i' was previously used to select IQ mode. Now use 'q' instead. Type 'h' or '?' to see the complete keyboard shortcut help panel.

-

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

-

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

-

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

Elite: good point. What I can do is add an little icon and "20 kHz" to the last line of the listing along side the software version, GPS and antenna switch indicators. You can't rely on the user count saying "N / 3 users" to mean the Kiwi is in 3 channel, 20 kHz mode because the "3 users" number might simply be a 4 channel, 12 kHz Kiwi with one channel password protected (which is not reflected in the count). -

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

Three channels at 20 kHz is subject to being reduced to only two depending on experiences with stability. I would have set it at two but I couldn't get the FPGA code to compile using only two channels for reasons I still don't understand. From the CHANGE_LOG file:v1.250 December 31, 2018 Add 20 kHz wide audio bandwidth mode. A third entry to the list of FPGA configurations. See admin "mode" tab for details. Add Ethernet 10/100 speed select to admin network tab. The speed changes after a few seconds of delay (no Kiwi restart required). This allows you to be looking at a waterfall in another window and see if the Ethernet spurs (if present at your installation) improve or not. Be sure the device (router, switch) your Kiwi connects to supports 10 Mbps Ethernet. Accept 'k' & 'M' scaling suffixes in frequency and passband parameters. Examples: Type "/15k" in frequency box to get a 15 kHz wide passband. Or "/2.7k", "-5k,10k" etc. Use a URL of "...?f=7.4M/16.5k" to set a frequency of 7.4 MHz and passband of 16.5 kHz. Note uppercase 'M' since 'm' is already keyboard shortcut for mute. You can remember this because the 'M' in MHz is always capitalized whereas 'k' in kHz is not. Note also 'k' used to be paired with 'j' as the frequency up/down jog shortcut. Now use the 'j' and 'i' keys are used (also 'J' and 'I' to jog faster). Using the 'i' key is actually more natural because it fits the placement of your index and middle fingers better than 'j' and 'k'. Finally, 'i' was previously used to select IQ mode. Now use 'q' instead. Type 'h' or '?' to see the complete keyboard shortcut help panel.

-

v1.250: 20 kHz bandwidth mode, 10/100 Ethernet speed selection, k/M frequency/passband suffixes

Elite: good point. What I can do is add an little icon and "20 kHz" to the last line of the listing along side the software version, GPS and antenna switch indicators. You can't rely on the user count saying "N / 3 users" to mean the Kiwi is in 3 channel, 20 kHz mode because the "3 users" number might simply be a 4 channel, 12 kHz Kiwi with one channel password protected (which is not reflected in the count).